Associate Professor MIYAMA Masayuki

Faculty, Affiliation

Advanced Mobility Research Institute

College and School Educational Field

Division of Electrical Engineering and Computer Science, Graduate School of Natural Science and Technology

Division of Electrical Engineering and Computer Science, Graduate School of Natural Science and Technology

Course in Information and Communication Engineering, School of Electrical, Information and Communication Engineering, College of Science and Engineering

Laboratory

Multimedia Integrated Circuit System Laboratory TEL:076-234-4862 FAX:076-234-4870

Academic Background

【Academic background(Doctoral/Master's Degree)】

Japan Advanced Institute of Science and Technology Master 1995 Completed

【Academic background(Bachelor's Degree)】

University of Tsukuba 198803

【Degree】

Master of Engineering

Career

Year & Month of Birth

1966/03

Academic Society

IEEE

Award

○IP Award(2008/04/24)

○IP Award(2008/04/24)

○IP Award(2008/04/24)

Specialities

Electron device/Electronic equipment

Speciality Keywords

VLSI, Image Processing, Electronic Design Automation

Research Themes

Study on VLSI Image Processing

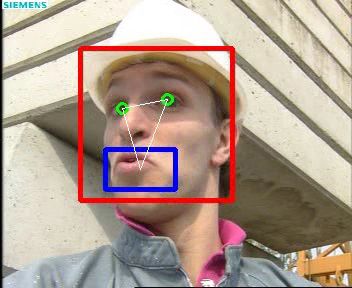

Topic 1: VLSI Image Analysis and Understanding

Topic 1: VLSI Image Analysis and Understanding

Topic 2: VLSI Image Coding

Topic 3: VLSI Image Restoration and Reconstruction

Study on Electronic Design Automation

Books

Papers

- An Ultra Low Power, Realtime MPEG2 MP@HL Motion Estimation Processor Core with SIMD Datapath Architecture Optimized for Gradient Descent Search Algorithm IEEE 2002 Custom Integrated Circuits Conference 167-170 2002/05

- An Image Sensor With Fast Objects Positions Extraction Function IEEE TRANSACTIONS ON ELECTRON DEVICES 50 1 184-190 2003/01

- A Feed-Forward Dynamic Voltage Control Algorithm for Low Power/High Quality MPEG4 on Multi-regulated Voltage CPU 0 0 0 2003/04

- An Ultra Low Power Motion Estimation Processor for MPEG2 HDTV Resolution Video IEICE TRANSACTIONS ON ELECTRONICS VOL.E86-C 4 561-569 2003/05

- A Sub-mW MPEG-4 Motion Estimation Processor Core for Mobile Video Application 0 0 181-184 2003/09

- A Sub-mW MPEG-4 Motion Estimation Processor Core for Mobile Video Application 0 0 527-528 2004/01

- A Feed-Forward Dynamic Voltage Control Algorithm for Low Power MPEG4 on Multi-Regulated Voltage CPU IEICE TRANSACTIONS ON ELECTRONICS E87-C 4 457-465 2004/04

- VLSI-Oriented Motion Estimation Using a Steepest Descent Method in Mobile Video Coding IEICE TRANSACTIONS ON ELECTRONICS E87-C 4 464-474 2004/04

- A Feed-Forward Dynamic Voltage Frequency Management for Power-minimum Motion Video Compression in Sub-Decimicron Era K.Kawakami,M.Kanamori,Y.Morita,J.Takemura,H.Ohira,M.Miyama,M.Yoshimoto Sixth Biannual World Automation Congress (WAC) 2004/06

- A Sub-mW MPEG-4 Motion Estimation Processor Core for Mobile Video Application IEEE JOURNAL OF SOLID-STATE CIRCUITS 39 9 1562-1570 2004/09

- A Low-Power Systolic Array Architecture for Block-Matching Motion Estimation J.Miyakoshi, Y.Murachi, K.Hamano, T.Matsuno, M.Miyama, M.Yoshimoto IEICE TRANSACTIONS ON ELECTRONICS 88 4 559-569 2005/04

- A 95 mW MPEG2 MP@HL Motion Estimation Processor Core for Portable High-Resolution Video Application Y.Murachi,K.Hamano,T.Matsuno,J.Miyakoshi,M.Miyama,M.Yoshimoto 2005 Symposium on VLSI Circuits Digest of Technical papers 212-215 2005/06

- A Wireless-Interface SoC Powered by Energy Harvesting for Short-range Data Communication S.Mikami,T.Matsuno,M.Miyama,M.Yoshimoto,H.Ono A-SSCC 2005 Proceedings of Technical Papers 241-244 2005/11

- A 95 mW MPEG2 MP@HL Motion Estimation Processor Core for Portable High-Resolution Video Application Y.Murachi, K.Hamano, T.Matsuno, J.Miyakoshi, M.Miyama, M.Yoshimoto IEICE TRANSACTIONS ON FUNDAMENTALS OF ELECTRONICS COMMUNICATIONS AND COMPUT 88 12 3492-3499 2005/12

- Power-Minimum Frequency / Voltage Cooperative Management Method for VLSI Processor in Leakage-dominant Technology Era K.Kawakami, M.Kanamori, Y.Morita, J.Takemura, M.Miyama, M.Yoshimoto IEICE TRANSACTIONS ON FUNDAMENTALS OF ELECTRONICS COMMUNICATIONS AND COMPUT 88 12 3290-3297 2005/12

- A Feed-Forward Dynamic VDD-VBB-Frequency Management for Low Power Motion Video Compression on 90nm RISC Processor K. Kawakami, M. Kananmori, Y. Morita, J. Takemura, H. Ohira, M. Miyama, M. Yoshimoto Intelligent Automation and Soft Computing (AutoSoft Journal 12 3 283-298 2006/01

- An Architecture Study of Scalable Optical-Flow Processor for Real-Time Video Segmentation Ryo Yamamoto, Yuki Fukuyama, Tadayoshi Katagiri, Junichi Miyakoshi, Yuki Kuroda, Noriyuki Minegishi, Masayuki Miyama, Hiroshi Kawaguchi, Kousuke Imamura, Hideo Hashimoto, and Masahiko Yoshimoto CoolChips 2006 2006/04

- An Energy-Harvesting Wireless-Interface SoC for Short-Range Data Communication S. Mikami, T. Matsuno, M. Miyama, H. Kawaguchi, M. Yoshimoto, and H. Ono IEEJ Trans. Electronics, Information and Systems 126 5 565-570 2006/05

- High-Quality-Image Compression System for Short-Delay and Real-Time Wireless Transmission M. Nakao, M. Kita, M. Miyama, SID 2006 2006/06

- VLSI Architecture Study of a Real-Time Scalable Optical Flow Processor for Video Segmentation N. Minegishi, J. Miyakoshi, Y. Kuroda, T. Katagiri, Y. Fukuyama, R. Yamamoto, M. Miyama, K. Imamura, H. Hashimoto, and M. Yoshimoto 89 3 230-242 2006/05

- Dynamic Reconfigurable Variable-Length Processor Core with 30 fr/s HDTV to H.264, MPEG-2 and MPEG-4 89 6 1091-1100 2006/06

- An 800-uW H.264 Baseline-Profile Motion Estimation Processor Core T. Iinuma, J. Miyakoshi, Y. Murachi, T. Matsuno, M. Hamamoto, T.Ishihara, H. Kawaguchi, M. Miyama, and M. Yoshimoto 2006 IEEE Asian Solid-State Circuits Conference 2006/11

- A Sub-mW H.264 Baseline-Profile Motion Estimation Processor Core with a VLSI-Oriented Block Partitioning Strategy and SIMD/Systolic-Array Architecture J. Miyakoshi, Y. Murachi, T. Matsuno, M. Hamamoto, T. Iinuma, T. Ishihara, H. Kawaguchi, M. Miyama and M. Yoshimoto 89 12 0-0 2006/12

- A 158 MS/S JPEG 2000 CODEC WITH A BIT-PLANE AND PASS PARALLEL EMBEDDED BLOCK CODER M.Miyama, Y.Inoie, T.Kasuga, R.Inada, R.Kawai, M.Nakao, Y.Matsuda Picture Coding Symposium 2007 2007/11

- A VGA 30-fps Optical-Flow Processor Core Based on Pyramidal Lucas and Kanade Algorithm H.Ishihara, M.Miyama, Y.Matsuda, Y.Murachi, Y.Fukuyama, R.Yamamoto, J.Miyakoshi, H.kawaguchi, and M.Yoshimoto A-SSCC2007 2007/11

- A 8ms Delay Image Transmission System and Its Applications Haifeng Chen, Masashi Nakao, Masayuki Miyama IDW '07 - Proceedings of the 14th International Display Workshops 1425-1428 2007/12

- A VGA 30-fps Realtime Optical-Flow Processor Core for Moving Picture Recognition Y. Murachi, H. Ishihara, Y. Fukuyama, R. Yamamoto, M. Miyama,H. Kawaguchi, Y. Matsuda, and M. Yoshimoto IEICE TRANSACTIONS ON ELECTRONICS E91-C 4 457-464 2008/04

- A 158 MS/s JPEG 2000 Codec with a Bit-Plane and Pass Parallel Embedded Block Coder for Low Delay Image Transmission Masayuki MIYAMA, Yuusuke INOIE, Takafumi KASUGA, Ryouichi INADA, Masashi NAKAO, Yoshio MATSUDA IEICE TRANSACTIONS ON FUNDAMENTALS OF ELECTRONICS COMMUNICATIONS AND COMPUT E91-A 8 2025-2034 2008/08

- A VGA 30 FPS Affine Motion Estimation Processor for Real-Time Video Segmentation Y. Yunbe, M. Miyama, and Y. Matsuda IASTED Circuits and Systems Conference Proceedings 2008/08

- Performance Enhancement of a Fast H.264/AVC Intra-Prediction Algorithm using Directional Masks J91-D 9 - 2008/09

- A Charge Recycling TCAM with Checkerboard Array Arrangement for Low Power Applications Takahito Kusumoto, Daisuke Ogawa, Katsumi Dosaka, Masayuki Miyama, and Yoshio Matsuda Proceeding of ASSCC 2008 2008/11

- A VLSI Architecture for VGA 30 fps Video Segmentation with Affine Motion Model Estimation Masayuki Miyama, Yoshiki Yunbe, Kouji Togo, Yoshio Matsuda Proceeding of International Symposium on Integrated Circuit 2009 2009/12

- Affine Motion Model Estimation processor for Real-Time Video Segmentation 2010/03

- Fast Algorithm and Architecture for H.264/AVC Intra Frame Coder J93-D 4 443-452 2010/04

- A Complete Charge Recycling TCAM with Checkerboard Array Arrangement for Low Power Applications Katsumi DOSAKA, Daisuke OGAWA, Takahito KUSUMOTO, Masayuki MIYAMA, and Yoshio MATSUDA IEICE TRANSACTIONS ON ELECTRONICS E93-C 5 685-695 2010/05

- Model-based SoC design using ESL environment Dai ARAKI, Atsushi NAKAMURA, Masayuki MIYAMA 2010/11

- A VGA 30 fps Affine Motion Model Estimation VLSI for Real-Time Video Segmentation Yoshiki YUNBE, Masayuki MIYAMA, Yoshio MATSUDA IEICE TRANSACTIONS ON INFORMATION AND SYSTEMS E93D 12 3284-3293 2010/12

- Vehicle Detection and Tracking with Affine Motion Segmentation in Stereo Video Masayuki Miyama, Yoshio Matsuda IEEE International Conference on Signal and Image Processing Applications 2011 2011/11

- Frame Rate Up-conversion Using HOE (Hierarchical Optical flow Estimation) Based Bidirectional Optical Flow Estimation Mamoru Ogaki, Tetsuya Matsumura, Koji Nii, Masayuki Miyama, Kousuke Imamura and Yoshio Matsuda International Journal of Computer Science and Network Security 12 6 52-61 2012/06

- Integrated Face Detection, Tracking, and Pose Estimation MIYAMA,Masayuki, MATSUDA,Yoshio International Conference on Signal Processing 2012/10

- Fast Vehicle Detection System Using Statistics of Gradient Images as Image Features Masayuki MIYAMA IIEEJ Transactions on Image Electronics and Visual Computing 3 2 206-214 2015/12/21

- Fast Face Detection with Multi-Scale Window Search Free from Image Resizing Using SGI Features Masayuki Miyama Journal of Computer and Communications 4 22-29 2016/08/10

- FAST SUPER-PIXEL SEGMENTATION WITH CLEAR DETAIL AND SHORT BOUNDARY Masayuki Miyama Proceeding of the 5th IIEEJ International Workshop on Image Electronics and Visual Computing 2017/02/28

- A High Efficient Multi-Scale Multi-Target Object Detection Processor Using SGI Features Masayuki MIYAMA IIEEJ Transactions on Image Electronics and Visual Computing 5 1 10-19 2017/06/19

- Fast Stereo Matching with Super-pixels Using One-way Check and Score Filter Masayuki Miyama Proceeding of the 7th IEEE International Conference on Control Systems, Computing and Engineering 2017/11/24

- FPGA Accelerator for Super-pixel Segmentation Featuring Clear Detail and Short Boundary Masayuki MIYAMA IIEEJ Transactions on Image Electronics and Visual Computing 5 2 83-91 2017/12/20

- Fast Stereo Matching Fully Utilizing Super-Pixels Masayuki Miyama Journal of Computer and Communications 6 8 2018/08/02

- HD 180 FPS FPGA Processor to Generate Depth Image with Clear Object Boundary Masayuki Miyama Proceedings of International Symposium on Devices, Circuits and Systems 2019/03/06

- Convolutional Network for Generic Object Contour Detection with Stereo Vision Masayuki Miyama Proceedings of the 2019 2nd International Conference on Information Hiding and Image Processing 25-29 2019/09

- FPGA implementation of 3-bit quantized CNN for semantic segmentation MIYAMA, Masayuki Proceedings of the 2020 4th International Conference on Circuits, Systems and Devices 2020/10/25

- FPGA Implementation of 3-Bit Quantized Multi-Task CNN for Contour Detection and Disparity Estimation Masayuki MIYAMA IEICE TRANSACTIONS on Information and Systems No.2 pp.406-412 2022/02/01

- Robust Inference of Multi-Task Convolutional Neural Network for Advanced Driving Assistance by Embedding Coordinates Masayuki Miyama Proceedings of the 8th World Congress on Electrical Engineering and Computer Systems and Sciences (EECSS'22) 2022/07/30

- The FOD Detection Based on Modified SSD for Small Object Tirakitpanitchakorn Atthawut,深山 正幸 2022/09/03

- REAL-TIME EMBEDDED SYSTEM OF MULTI-TASK CNN FOR ADVANCED DRIVING ASSISTANCE Masayuki Miyama INTERNATIONAL JOURNAL OF ADVANCES IN SIGNAL AND IMAGE SCIENCES Vol. 9 No.2 pp.29-45 2023/12/30

- PaintedPillars: Efficient 3D Object Detection Using Only Statistical Processing To Compute Pillar Features with Explicit Class Probability Distributions Masayuki Miyama Proceedings of the 10th World Congress on Electrical Engineering and Computer Systems and Sciences (EECSS'24) 2024/08/19

- 3D Semantic Segmentation for Autonomous Driving Using Late Fusion of LiDAR Range Images and Camera Images with Simple 2D Transformation M.Miyama Proceedings Volume Seventh International Conference on Image, Video Processing, and Artificial Intelligence (IVPAI 2025) 13731 1373106 2025/05/18

Conference Presentations

- FPGA Design with OpenCL(2017/03/07)

Others

- VGA 91 fps@94 MHz Affine Motion Segmentation Processor 26 4 1-7 2015/04/10

Arts and Fieldwork

Patent

Theme to the desired joint research

○VLSI Image Processing

Grant-in-Aid for Scientific Research

○「実時間高精細動画像処理プロセッサLSIの研究」(2001-2002)

○「実時間モデルベース動領域抽出VLSIプロセッサの研究」(2007-2009)

○「確率的領域分割と超平面クラス分類による高精度・汎用・実時間画像認識SOCの研究」(2010-2012)

○「スーパーピクセルと視差モデルを用いた高密度・高精度な実時間距離画像生成回路の開発」(2015-2017)

○「SLAM用意味分割・距離推定・動き推定の実時間同時処理1チップCNN回路開発」(2018-2020)

○「自動運転向け周囲環境認識用実時間組込みAIシステムの高精度・低電力化」(2024-2026)

Competitive research funding,Contribution

Collaborative research,Consignment study

○Study on optical communication system using POF(2000-2000)

○Study on low power motion estimation VLSI for image compression(2002-2003)

○Study on real-time video recognition VLSI(2004-2006)

○Study on image coding VLSI(2004-2007)

○Study on low power CAM system(2006-2006)

○Study on Image Restoration(2009-2009)

Classes (Bachelors)

○Computer System B(2025)

○Information and Communication Engineering Laboratory III(2025)

○Advanced Topics on Information & Communication Engineering A(2025)

○Student-Initiated Project(2025)

○Student-Initiated Project(2025)

○Information and Communication Engineering Laboratory III(2025)

○Integrated Circuit D(2025)

○Student-Initiated Project(2025)

○Operating System B(2025)

○Logical Circuit B(2025)

○Integrated Circuit C(2025)

○Operating System A(2025)

○Computer System A(2025)

○Logical Circuit B(2025)

○Information and Communication Engineering Laboratory III(2025)

○Logical Circuit A(2025)

○Logical Circuit A(2025)

○Operating Systems B(2025)

○Operating Systems A(2025)

○Introduction to Data Science(2025)

○Introduction of Electric, Communication, and Information Engineering(2024)

○Information and Communication Engineering Laboratory III(2024)

○Student-Initiated Project(2024)

○Student-Initiated Project(2024)

○Information and Communication Engineering Laboratory III(2024)

○Advanced Topics on Information & Communication Engineering A(2024)

○Computer System B(2024)

○Computer System A(2024)

○Logical Circuit B(2024)

○Logical Circuit A(2024)

○Introduction to Data Science(2024)

○Introduction of Electric, Communication, and Information Engineering(2023)

○Student-Initiated Project(2023)

○Computer System B(2023)

○Advanced Topics on Information & Communication Engineering A(2023)

○Student-Initiated Project(2023)

○Information and Communication Engineering Laboratory III(2023)

○Computer System A(2023)

○Logical Circuit B(2023)

○Information and Communication Engineering Laboratory III(2023)

○Logical Circuit A(2023)

○Specialized Seminar(2023)

○Specialized Seminar(2023)

○Introduction to Data Science(2023)

○Introduction of Electric, Communication, and Information Engineering(2022)

○Student-Initiated Project(2022)

○Computer System A(2022)

○Information and Communication Engineering Laboratory III(2022)

○Advanced Topics on Information & Communication Engineering A(2022)

○Computer System B(2022)

○Student-Initiated Project(2022)

○Information and Communication Engineering Laboratory III(2022)

○Logical Circuit B(2022)

○Logical Circuit A(2022)

○Introduction to Data Science(2022)

○Lecture on Life in Campus and Society(2021)

○Lecture on Life in Campus and Society(2021)

○Introduction to Data Science(2021)

○Computer System A(2021)

○Research Project(2021)

○Logical Circuit A(2021)

○Student-Initiated Project(2021)

○Information and Communication Engineering Laboratory III(2021)

○Computer System B(2021)

○Research Project(2021)

○Advanced Topics on Information & Communication Engineering A(2021)

○Logical Circuit B(2021)

○Advanced Topics on Information & Communication Engineering A(2020)

○Communication and Computer System Engineering Laboratry III(2020)

○Computer System A(2020)

○Specialized Experiment(2020)

○Specialized Research(2020)

○Introduction to Date Science(2020)

○Logical Circuit B(2020)

○Communication Systems A(2020)

○Logical Circuit A(2020)

○Visi Design & Practice B(2020)

○Visi Design & Practice A(2020)

○Research Project(2020)

○Machine Learning B(2020)

○Machine Learning A(2020)

○Student-Initiated Project(2020)

○Computer System B(2020)

○Communication Systems B(2020)

○Lecture on Life in Campus and Society(2020)

○Lecture on Life in Campus and Society(2020)

○Visi Design & Practice B(2019)

○Logical Circuit A(2019)

○Logical Circuit B(2019)

○Computer System A(2019)

○Electrical and Electronic Engineering Laboratory III(2019)

○Introduction to Information Technology(2019)

○Computer System B(2019)

○Electrical and Electronic Engineering Laboratory II(2019)

○Vlsi Design & Practice(2019)

○Internships A(2019)

○Internships B(2019)

○Visi Design & Practice A(2019)

○Electrical and Electronic Engineering Laboratory II(2018)

○Introduction to Computer Programming(2018)

○Logical Circuit(2018)

○Introduction to Information Technology(2018)

○Electrical and Electronic Engineering Laboratory III(2018)

○Vlsi Design & Practice(2018)

○Electrical and Electronic Engineering Laboratory III(2017)

○Vlsi Design & Practice(2017)

○Presentation and Debate (Freshman Seminar II)(2017)

○Presentation and Debate (Freshman Seminar II)(2017)

○Presentation and Debate (Freshman Seminar II)(2017)

○Freshman Seminar I(2017)

○Freshman Seminar I(2017)

○Logical Circuit(2017)

○Presentation and Debate (Freshman Seminar II)(2017)

○Introduction to Computer Programming(2017)

○Electrical and Electronic Engineering Laboratory II(2017)

○Freshman Seminar I(2016)

○Presentation and Debate (Freshman Seminar II)(2016)

○Freshman Seminar I(2016)

○Presentation and Debate (Freshman Seminar II)(2016)

○Electrical and Electronic Engineering Laboratory III(2016)

○Electrical and Electronic Engineering Laboratory II(2016)

○Logical Circuit(2016)

○Vlsi Design & Practice(2016)

○Logical Circuit(2011)

○Electrical and Electronic Engineering Laboratory II(2011)

○Vlsi Design Laboratory(2011)

○Introduction to Computer Programming(2011)

○Electrical and Electronic Engineering Laboratory III(2011)

○Logical Circuit(2010)

○Electrical and Electronic Engineering Laboratory II(2010)

○Vlsi Design Laboratory(2010)

○Introduction to Computer Programming(2010)

○Electrical and Electronic Engineering Laboratory III(2010)

Classes (Graduate Schools)

○Advanced VLSI Image Processing(2025)

○Advanced VLSI Image Processing(2025)

○Laboratory Rotation I(2025)

○SoC Design Fundamentals A(2025)

○SoC Design Fundamentals B(2025)

○Advanced VLSI Image Processing(2024)

○Advanced VLSI Image Processing(2024)

○Laboratory Rotation I(2024)

○Laboratory RotationⅠ(2024)

○Laboratory RotationⅠ(2024)

○SoC Design Fundamentals B(2024)

○SoC Design Fundamentals A(2024)

○Advanced VLSI Image Processing(2023)

○Advanced VLSI Image Processing(2023)

○Laboratory Rotation I(2023)

○Laboratory Rotation I(2023)

○Laboratory Rotation I(2023)

○Laboratory RotationⅠ(2023)

○Laboratory RotationⅠ(2023)

○Laboratory RotationⅠ(2023)

○Laboratory RotationⅠ(2023)

○SoC Design Fundamentals A(2023)

○SoC Design Fundamentals B(2023)

○SoC Design Fundamentals B(2023)

○SoC Design Fundamentals A(2023)

○Laboratory Rotation I(2023)

○Introduction to Electrical Engineering and Computer Science(2022)

○Advanced VLSI Image Processing(2022)

○Introduction to Electrical Engineering and Computer Science(2022)

○Advanced VLSI Image Processing(2022)

○SoC Design Fundamentals B(2022)

○SoC Design Fundamentals A(2022)

○SoC Design Fundamentals(2022)

○SoC Design Fundamentals A(2022)

○SoC Design Fundamentals B(2022)

○SoC Design Fundamentals(2022)

○SoC Design Fundamentals A(2021)

○Research Ethics(2021)

○Introduction to Electrical Engineering and Computer Science(2021)

○Introduction to Electrical Engineering and Computer Science(2021)

○Introduction to Electrical Engineering and Computer Science(2021)

○Research Ethics(2021)

○SoC Design Fundamentals B(2021)

○SoC Design Fundamentals B(2020)

○SoC Design Fundamentals A(2020)

○Research Ethics(2020)

○Research Ethics(2020)

○Advanced VLSI Image Processing(2020)

○Advanced VLSI Image Processing(2020)

○Advanced VLSI Image Processing(2020)

○Advanced VLSI Image Processing(2020)

○Fostering the independence of researchers(2020)

○Introduction to Electrical Engineering and Computer Science(2020)

○Exercise for Technical Intern(2020)

○Research Ethics(2019)

○Advanced VLSI Image Processing(2019)

○Advanced VLSI Image Processing(2019)

○Research Ethics(2019)

○SoC Design Fundamentals(2019)

○Fostering the independence of researchers(2019)

○Advanced VLSI Image Processing(2019)

○Exercise for Technical Intern(2019)

○Advanced VLSI Image Processing(2019)

○SoC Design Fundamentals(2018)

○Advanced VLSI Image Processing(2018)

○Advanced VLSI Image Processing(2017)

○SoC Design Fundamentals(2017)

○Advanced VLSI Image Processing(2017)

○Advanced VLSI Image Processing(2017)

○Advanced VLSI Image Processing(2017)

○Advanced VLSI Image Processing(2016)

○SoC Design Fundamentals(2016)

○Embedded System Engineering(2012)

○SoC Design Fundamentals(2012)

○Vlsi Design Automation(2012)

○VLSI System Design(2010)

○Electric Power Systems Engineering(2010)